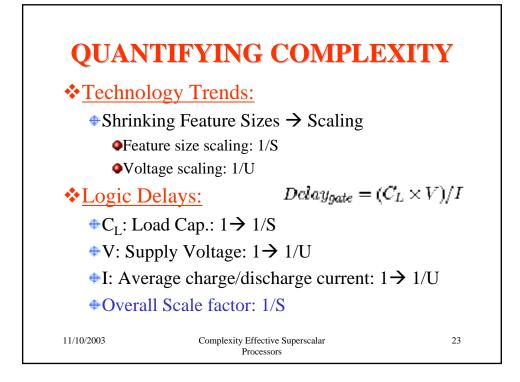

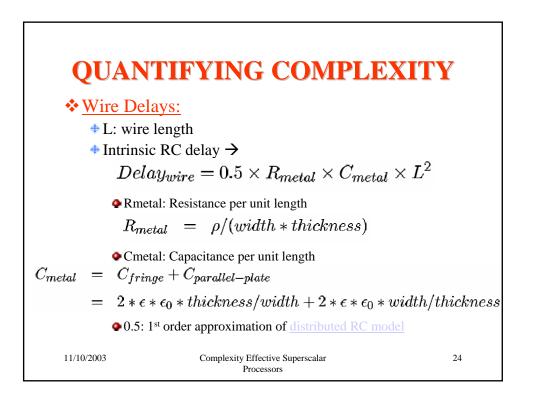

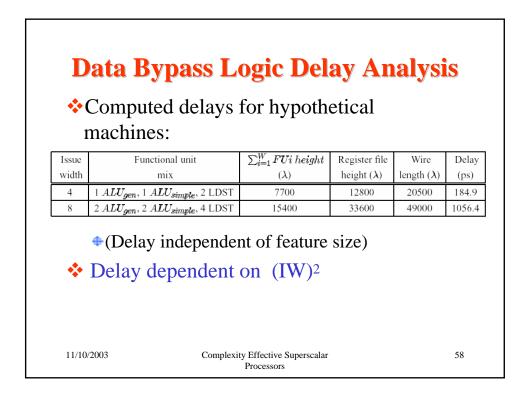

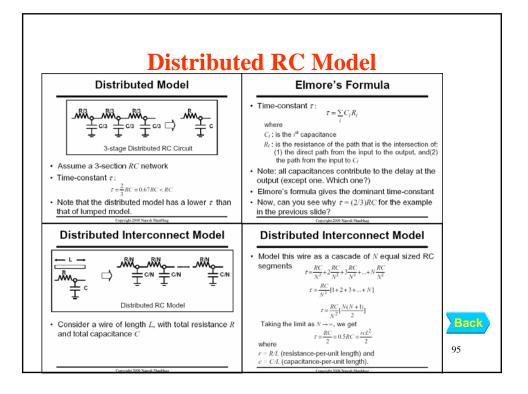

| Delay → Gei                                                                             | neric w                                           | vire delay:                                                                         |

|-----------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------|

|                                                                                         |                                                   | $_{ire} = 0.5 \times R_{metal} \times C_{metal} 	imes$                              |

| ⊕L is depende                                                                           | ent on #                                          | t of FUs (IW) & FU heights                                                          |

| • D' 1' 1                                                                               |                                                   |                                                                                     |

| Pipeline dep                                                                            | th 🖊 尹                                            | C / <not implemented="" in="" simulations!<="" th=""></not>                         |

| • Typical FU hei                                                                        |                                                   | C <b>オ</b> <not implemented="" in="" simulations!<="" th=""></not>                  |

| 1 1                                                                                     |                                                   | C C  NOT implemented in simulations! Description                                    |

| • <u>Typical FU hei</u>                                                                 | <u>ghts:</u>                                      | -                                                                                   |

| Typical FU hei                                                                          | ghts:<br>Height $(\lambda)$                       | Description                                                                         |

| Typical FU hei<br>Functional unit<br>Adder                                              | <b>ghts:</b><br>Height (λ)<br>1400                | Description<br>64-bit adder                                                         |

| Functional unit Adder Shifter                                                           | <b>ghts:</b><br>Height (λ)<br>1400<br>1500        | Description<br>64-bit adder<br>64-bit barrel shifter                                |

| Typical FU hei         Functional unit         Adder         Shifter         Logic Unit | <b>ghts:</b><br>Height (λ)<br>1400<br>1500<br>300 | Description<br>64-bit adder<br>64-bit barrel shifter<br>Performs logical operations |

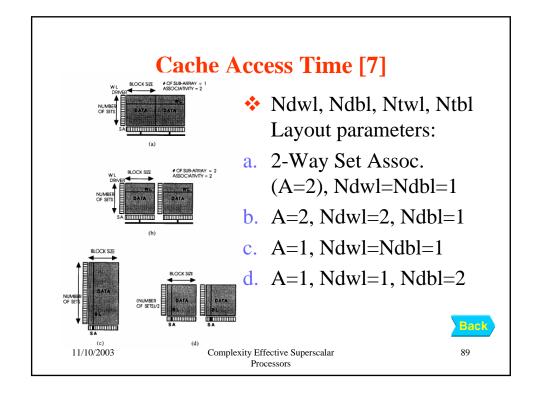

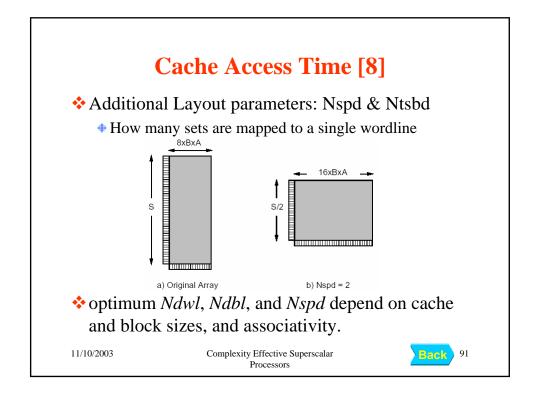

| Symbols                                                                  | Meanings                                                                                                                                                                                                                                                                                                 | Parameters & Equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B<br>A<br>S<br>Ndwl<br>Ndbl<br>Ntwl<br>Ntwl<br>Rows<br>Cols<br>Subs<br>C | Block size<br>Associativity<br>Number of sets<br># of segments per word line (data)<br># of segments per bit line (data)<br># of segments per bit line (tag)<br># of segments per bit line (tag)<br>Number of rows in a subarray<br>Number of columns in a subarray<br>Number of subarrays<br>Cache size | 4, 8, 16, and 32 bytes         1, 2, 4, 8         256, 512, 1K, 2K, 4K, 8K, 16K         1, 2, 4, $\cdots$ 1, 2, 4, $\cdots$ 1, 2, 4 $\cdots$ 1, 4 $\cdots$ |

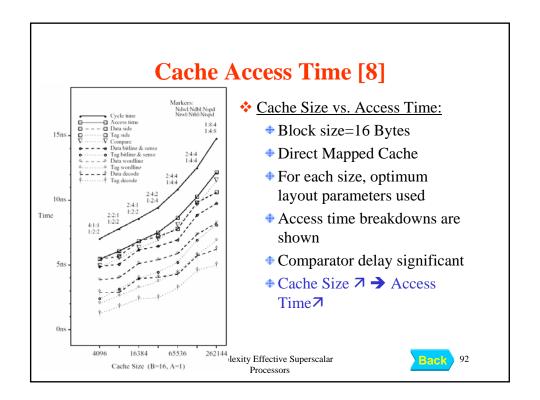

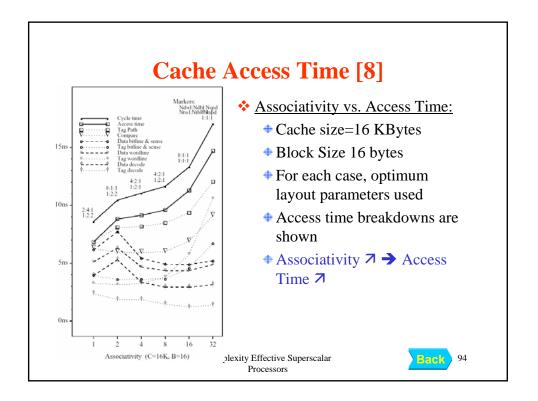

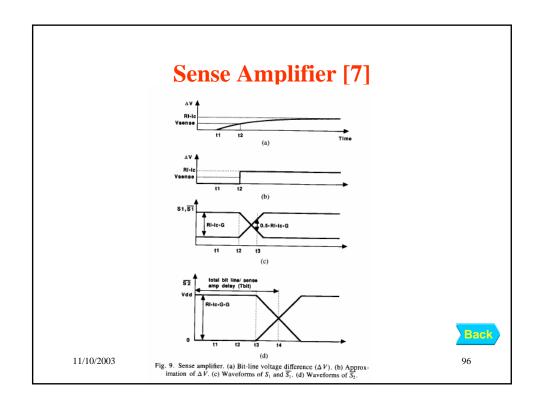

| <ul><li>Acce</li></ul>                                                   | l, Ndbl, Ntwl, Ntbl → Layout p<br>ss Time = Decoder Delay + Wo<br>lifier Delay + Data Bus Delay                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Form                                                                     | ula & Derivations in paper                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                          | breakdown plots not descriptiv<br>e Twl vs. (B.8).A/Ndwl                                                                                                                                                                                                                                                 | ve of cache parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | REFERENCES                                                                                                                                                                                                                                                       |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.    | S. Palacharla, N. Jouppi, and J. Smith, " <u>Complexity-Effective</u><br><u>Superscalar Processors</u> ", in Proceedings of the 24th<br>International Symposium on Computer Architecture, June<br>1997.                                                          |

| 2.    | S. Palacharla, N.P. Jouppi, and J.E. Smith, " <u>Quantifying the</u><br><u>Complexity of Superscalar Processors</u> ", Technical Report CS-<br>TR-96-1328, University of Wisconsin-Madison, November<br>1996.                                                    |

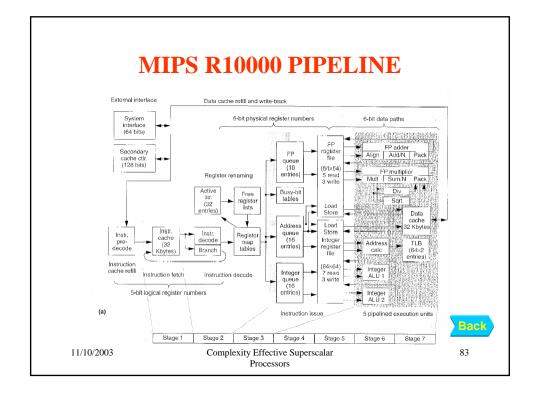

| 3.    | K. C. Yeager, " <u>MIPS R10000 Superscalar Microprocessor</u> ", <i>IEEE Micro</i> , April 1996.                                                                                                                                                                 |

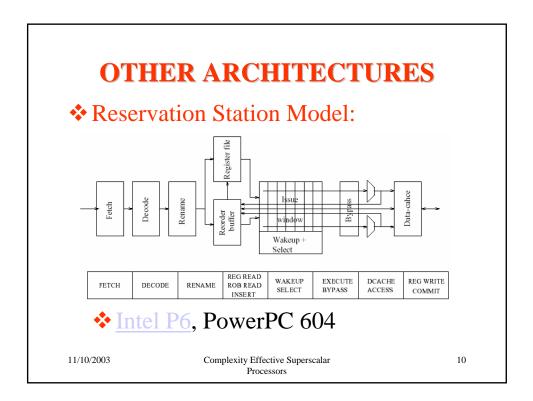

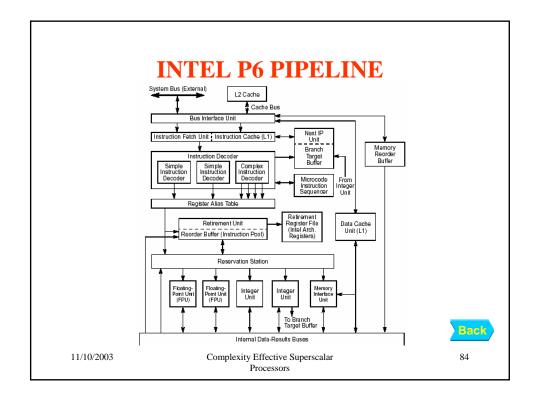

| 4.    | Linley Gwennap, "Intel's P6 Uses Decoupled Superscalar Design"<br><i>Microprocessor Report</i> , 9(2), February 1995.                                                                                                                                            |

| 5.    | Eric Rotenberg, Steve Bennet, and J. E. Smith. " <u>Trace Cache: a Low</u><br><u>Latency Approach to High Bandwidth Instruction Fetching</u> ",<br><i>Proceedings of the 29th Annual International Symposium on</i><br><i>Microarchitecture</i> , December, 1996 |

| 11/10 | /2003 Complexity Effective Superscalar 99<br>Processors 99                                                                                                                                                                                                       |